Understanding the relationship between a server processor (CPU) and its memory subsystem is critical when optimizing overall server performance. Every CPU generation has unique memory population guidelines that must be satisfied to attain the best memory performance.

2nd Generation AMD EPYCTM server processors can support up to sixteen memory modules across eight channels with two memory slots. This presents numerous possible ways of configuring the memory subsystem, yet there are only a couple of configurations that will achieve the peak memory performance for Dell EMC PowerEdge servers.

2nd Generation AMD EPYCTM server processors can support up to sixteen memory modules across eight channels with two memory slots. This presents numerous possible ways of configuring the memory subsystem, yet there are only a couple of configurations that will achieve the peak memory performance for Dell EMC PowerEdge servers.

Memory that has been incorrectly populated is referred to as an unbalanced configuration. From a functionality standpoint, an unbalanced configuration will operate adequately but will slow down memory data transfer speeds. Similarly, a near balanced configuration is also suboptimal. However, memory that has been correctly populated is referred to as a balanced configuration and will produce the best performance.

By following the guidelines below, customers can yield the highest memory performance of their memory modules:

- Memory Channel Population

- Balanced Configuration

- Memory slots must be fully populated with one or two DIMMs for best performance; a total of eight or sixteen DIMMs per CPU

- Near Balanced Configuration

- Populate four or more DIMMs per CPU

- Populate an even number of DIMMs per CPU

- Populate DIMMs in sequential order

- CPU and DIMM parts must be identical

- Each CPU must be identically configured with memory

Memory Channel Population

To achieve a balanced configuration, populate either eight or sixteen DIMMs per CPU. This allows the data traveling across memory modules to move most efficiently; utilizing the internal architecture of the AMD Rome CPU. Following this guideline will yield the highest memory bandwidth and the lowest memory latency.

If a balanced configuration of sixteen or eight DIMMs per CPU cannot be implemented, then the next best option is a near balanced configuration. Three guidelines must be satisfied to create a near balanced configuration.

◈ The first guideline is to populate a minimum of four DIMMS per CPU to ensure enough memory bandwidth exists for all Rome processor types.

◈ The second guideline is to never populate an odd number of DIMMs.

◈ The last guideline is that DIMMs must be populated in the intended order so that memory performance will be optimized across all the AMD CPU models.

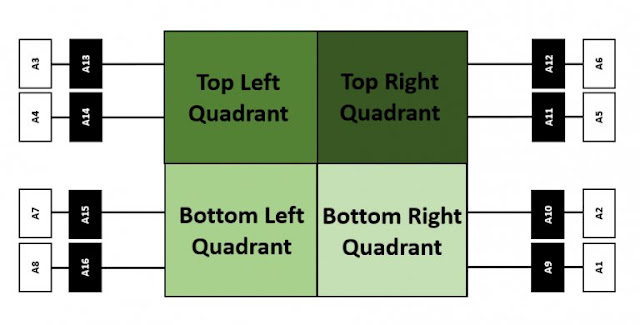

The figure below illustrates the assembly order in which individual DIMMs should be populated, starting with A1 and ending with A16:

Identical CPU and DIMM Parts

Identical memory modules must be used across all slots (i.e. same Dell part number). Dell EMC does not support memory mixing in Rome systems; only one memory model should exist within a CPU. This principle applies to the processors as well; multi-CPU Rome systems shall be populated with identical CPU models.

Identical Memory Configurations for Each CPU

Every CPU within a server must have identical memory configurations. When only one unique memory configuration exists across every CPU within a server, memory performance is further optimized.

Configuring for Maximum Performance

Balancing memory with 2nd Generation EPYCTM (Rome) server processors optimizes memory performance. When memory modules are configured in a balanced configuration, requested data traveling from the CPU to memory modules can perform most efficiently on Dell EMC PowerEdge servers.

0 comments:

Post a Comment